Bally Midway’s

"CHEAP SQUEAK"

Sound Module

AS-2518-45

(A080-91603-C000)

THEORY OF OPERATION

&

TROUBLESHOOTING

Copyright 2025 by Holger Stallmann (holli8123)

Dieses Dokument inkl. der Abbildungen ist urheberrechtlich geschützt.

Die Vervielfältigung, Bearbeitung, Verbreitung und jede Art der Verwertung außerhalb der Grenzen des Urheberrechtes bedürfen der schriftlichen Zustimmung des jeweiligen Autors bzw. Erstellers. Downloads und Kopien dieser Seite sind nur für den privaten, nicht kommerziellen Gebrauch gestattet.

Einleitung

Das CHEAP SQUEAK Board ist vom Leistungsumfang mit dem früheren Computer Sound Modul AS-2518-51 vergleichbar. Es bietet die Möglichkeit, einfache Töne, Geräusche und daraus zusammengesetzte Sounds zu generieren. Voice ist nicht implementiert. Erstmals tauchte die Schaltung des Cheap Squeak Boards 1981 als Bestandteil des Vidiot Module AS-2518-121 des Baby Pac-Man auf, der aus einem kombinierten Video Game und einem verkleinerten Flipper Spielfeld bestand. Die Schaltung des CHEAP SQUEAK wurde unter der Firmierung Bally Midway auf einem separaten Soundboard übernommen und als günstige Alternative zu dem, in vorherigen Geräten eingesetzten Squawk & Talk Board verbaut, was zuletzt auch der sich selbst auferlegten Low Budget Produktion geschuldet war.

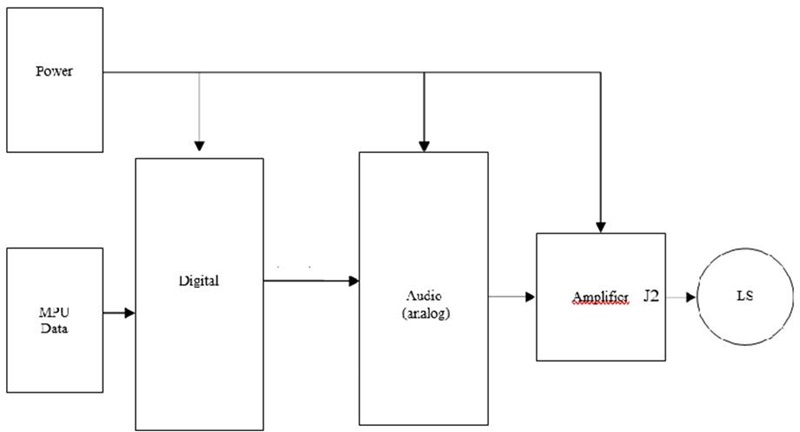

Blockschaltbild

Folgende Abbildung zeigt die einzelnen Funktionsblöcke, die im folgenden Artikel weiter in ihre einzelnen Bestandteile zerlegt und näher betrachtet werden.

- Spannungsversorgung und Spannungsregelung

- Ansteuerung durch die MPU

- Digitalteil mit CPU, Resetschaltung, ROM, digitalen Komponenten zur Soundgenerierung

- Audioteil mit den Komponenten zur Signalaufbereitung und Signalverstärkung

- Mono-Endstufe mit angeschaltetem Lautsprecher

Es wird empfohlen, den Schaltplan des Bally / Midway Cheap-Squeak sowie ein Board bzw. dessen Abbildung bereitzuhalten um die nachfolgenden Beschreibungen besser nachvollziehen zu können. Zusätzlich wird auf folgende Dokumente verwiesen, die zum Teil auch als Grundlage für die Beschreibungen in den folgenden Artikel hergenommen wurden:

- Bally / Midway Cheap-Squeak schematics

- Motorola MC6803 datasheets

- ZN429E-8 datasheet

- TDA2002 datasheet

Begriffsbestimmungen

- SB = CHEAP SQUEAK Soundboard

- MPU = 6800 Prozessor auf dem Rechnerboard des Flippers (nicht auf dem CHEAP SQUEAK)

- CPU = 680x Prozessor auf Position U1 des CHEAP SQUEAK

- RAM = Random Access Memory (Schreib- / Lesespeicher)

- ROM = Read only Memory (nur Lesespeicher)

- PIA = Peripheral Interface Adapter

- DAC = Digital-Analog Converter

- PSG = Programmable Sound Generator AY-3-8912

Schreibweisen

- Signale, die im aktivierten Zustand High-Pegel führen: Normale Schreibweise z.B. CA2

- Signale, die im aktivierten Zustand Low-Pegel führen: Mit vorangestelltem Schrägstrich z.B. /RESET

Fehler im Schaltplan

In den ersten Auflagen des Schaltplans sind einige Fehler enthalten, die im Laufe der Produktion korrigiert wurden:

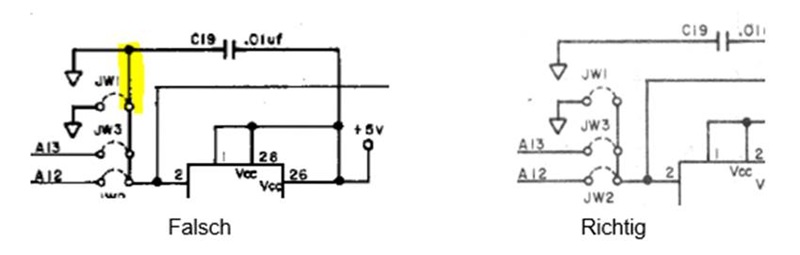

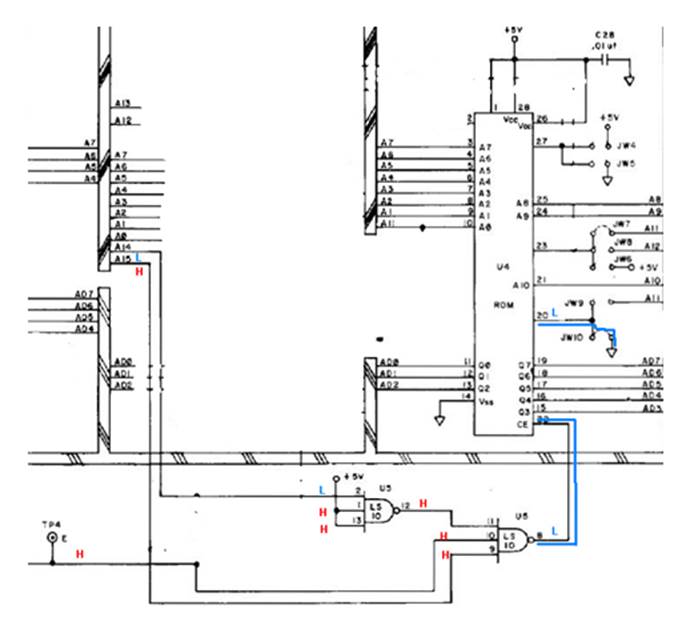

Jumper-Beschaltung im oberen Bereich von U3

Der folgende Ausschnitt aus dem Schaltplan kann so wie dargestellt nicht funktionieren. Durch die Jumper JW1, JW2 und JW3 soll je nach Bedarf der Pin 2 von beiden EPROM-Sockeln entweder mit GND oder mit A12 bzw. A13 verbunden werden können. Die gelb markierte Verbindung würde das verhindern und ist daher auf dem Platinen Layout nicht vorhanden.

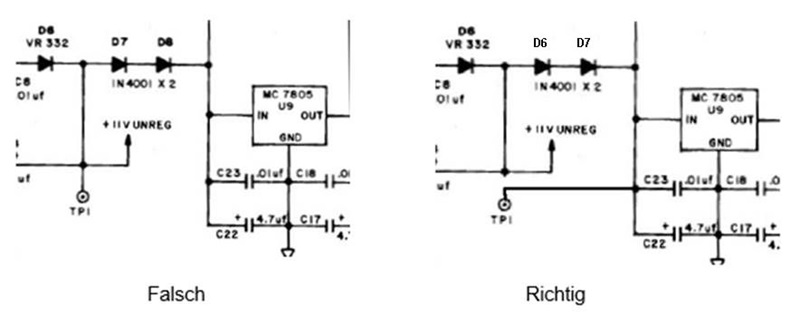

Position des TP1:

Die Verbindung zum TP1 ist im Schaltplan falsch angegeben. Auf dem Board ist TP1 mit dem Eingang des MC7805 verbunden.

IC-Übersicht des Digitalteil

Im Digitalteil des CHEAP SQUEAK Boards sind folgende ICs verbaut:

U1 - 8-bit Mikroprozessor Motorola MC6803 oder alternativ MC6801

U2 - Octal Latch 74LS373

U3 - 4kB oder 8kB (EP)ROM

U4 - 4kB (EP)ROM nur in Kombination mit 4kB (EP)ROM in U3

U5 - NAND-Gatter 74LS10 zur Adressdekodierung

U6 - Digital-Analog-Wandler ZN429E-8

6803 Adressbereiche

Der 6803 Mikroprozessor verwaltet einen Adressbereich von 64kB. Dieser Adressbereich ist auf dem CHEAP SQUEAK Board wie folgt aufgeteilt:

RAM: $0000-$007F

“Page Zero” RAM als interner Bestandteil der CPU.

Der Bereich $0000 bis $001F ist für die internen Register der CPU reserviert. $0020 - $007F stehen der Software als RAM zur Verfügung.

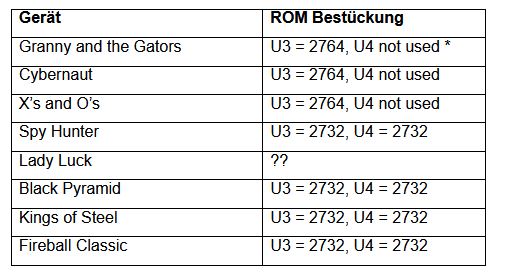

ROM

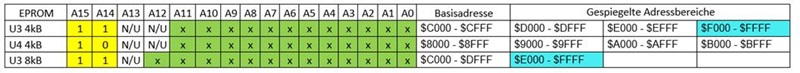

Je nach Gerätetyp werden zwei EPROMs mit einer Größe von 4kB (2532 oder 2732) oder ein EPROM mit einer Größe von 8kB (2764) eingesetzt.

Der ROM-Bereich ist im Adressraum der CPU wie folgt aufgeteilt:

$C000 - $CFFF : 4kB ROM auf Steckplatz U3

$C000 - $DFFF : 8kB ROM auf Steckplatz U3

$8000 - $8FFF : 4kB ROM auf Steckplatz U4

Hinweis:

Das Zusammenführen (Merging) der beiden 4kB Dateien für U3 und U4 zu einer 8kB großen Datei für ein Single-2764 in U3 funktioniert nicht, da ein 4kB U4 einen anderen Adressbereich belegt, als eine mit den 4kB von U4 programmierte Hälfte eines 8kB U3. Somit greifen die absoluten Sprungadressen im Programmablauf nicht.

Geräteübersicht

Das CHEAP SQUEAK wurde in folgenden Bally Midway Geräten verbaut:

Drahtbrücken-Kombinationen für verschiedene EPROMs

Die Code- / Sound-ROMs auf den gesockelten Positionen U3 und U4 sind gerätespezifisch. Die Adressierung für die jeweiligen EPROM-Typen und Größen (4kB oder 8kB) wird über Drahtbrücken (Jumper) eingestellt.

Jumper-Stellungen für die ROM-Adressierung:

2532 auf Position U3 und U4:

Jumper JW6, JW9, JW12 werden gesetzt

2732 auf Position U3 und U4:

Jumper JW7, JW10, JW11 werden gesetzt

Single 2764 auf Position U3:

Jumper JW2, JW4, JW7, JW11 werden gesetzt

Position U4 bleibt frei, daher hat ein evtl. ab Werk gesetzter JW10 keinen Einfluss

Ob die Möglichkeit besteht, ein Mischbetrieb aus 2532 und 2732 in U3 und U4 zu realisieren, ist nicht dokumentiert und muss ggf. rechnerisch ermittelt werden.

Hinweis: 2532 und 2732 EPROMs besitzen ein 24 Pin DIL Gehäuse. Diese müssen so in die 28 Pin DIL Fassungen gesetzt werden, dass sich Pin 1 des 24 Pin EPROMs auf Position 3 des Sockels befindet, sprich das EPROM unten bündig zum Sockel gesteckt ist.

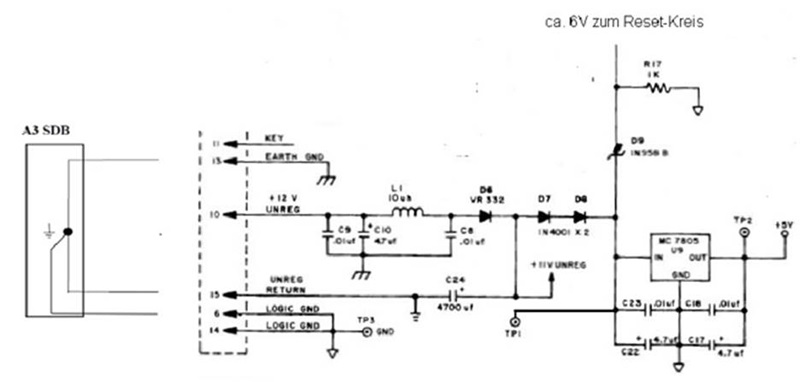

+12V und +5V Spannungsversorgung

Die Regelung der +5 Volt zur Versorgung der digitalen Logik und den Sound generierenden DAC wird durch den Spannungsregler MC7805 (U9) sichergestellt. Dieser befindet sich oberhalb von C24 auf dem größeren der beiden Kühlkörper.

Als Spannungsquelle bzw. Eingangsspannung des MC7805 dient die ungeregelte +12 Volt Versorgung, die durch das Solenoid Driver / Voltage Regulator Board an J1 Pin 10 (+12V unreg.) sowie Pin 15 (unreg. return) des CHEAP SQUEAK Boards bereitgestellt werden. Diese + 12 Volt versorgen zudem die Status-LED (s. Abb. 4). Die +12 Volt werden durch den hochkapazitiven Kondensator C14 (4700µ/25V) geglättet um unerwünschte Wechselspannungsanteile herauszufiltern um sie zusätzlich zur Versorgung der Vorverstärker- / Filterstufe um U7 und der 8 Watt Mono-Endstufe TDA2002 (U8) verwenden zu können.

Die genannten Spannungen liegen an folgenden Testpunkten an:

- +12 Volt an TP1

- +5 Volt an TP2

- GND an TP3

Sind weder die 11 V unreg. noch die +5V an den TP 1 und TP 2 messbar, ist zu prüfen, ob die 12V unreg. zwischen den Pins 10 und 15 an J1 anliegt. Ist das der Fall, ist L1, D6, D7 und D8 zu prüfen. Liegt 11V an TP1 und keine +5V an TP2, ist der MC7805 zu prüfen.

Die Sol Bus Return Leitung an J1-15 ist auf den Sound-Boards nicht mit der Board-Masse (Logic-GND) verbunden. Der zentrale Massepunkt befindet sich auf dem Solenoid Driver / Voltage Regulator Board A3, mit dem auch die Boardmasse (GND) über J1 Pin 6 (14) verbunden ist. Bei einer Unterbrechung der vom SDB kommenden Unreg. +5V Return Leitung arbeitet der Digitalteil vom Soundboard, allerdings fehlt die Masse für die Audio Komponenten und die Siebung der Versorgungsspannung durch den Kondensator C24 ist nicht mehr gegeben. Ob beide Verbindungen zum SDB bestehen, kann mit einer Widerstandsmessung bzw. Durchgangsprüfung zwischen TP3 (GND) und dem – Pol von C24 ermittelt werden. Eine überlagerte Wechselspannung kann zwischen TP1 und dem + Pol von C24 gemessen werden. Deren Wert soll 0.1 VAC nicht übersteigen.

Hinweis:

Im Fehlerfall sollten die Versorgungsspannungen nicht ausschließlich an den Testpunkten gemessen werden. Durch die doppelseitige und durchkontaktierte Platine wechseln die potential- und signalführenden Leiterbahnen häufig die Platinenseite. Wird bei einem Bauteiletausch die Durchkontaktierung beschädigt oder die Qualität der Lötstelle stellt den beidseitigen Kontakt nicht sicher, besteht die Gefahr, dass die Potentiale nicht an den Versorgungspins der IC oder an anderen Bauteilen anliegen. Zusätzlich zur Kontrolle an den Testpunkten wird eine direkte Messung an den Versorgungspins empfohlen, z.B.:

U1: +5V an Pin 7 gegen GND an Pin 1

U7: +11V an Pin 14 gegen GND an Pin 7

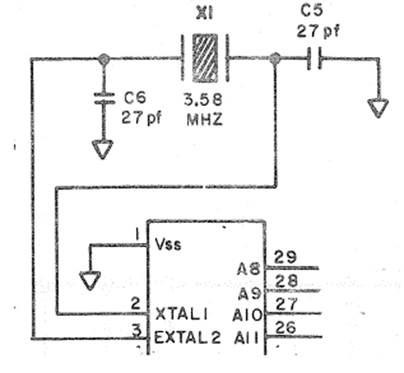

Takterzeugung

Die CPU benötigt zur Abarbeitung des Programmes einen Takt. Dieser wird durch einen 3.58 MHz Schwingquarz generiert, der an den Pins 2 und 3 angeschlossen ist und kann dort gemessen werden. Intern werden diese 3.58 Mhz durch 4 geteilt, so dass der eigentliche Systemtakt zum Abarbeiten der Befehle 895 kHz beträgt. Dieser Takt wird an Pin 40 (E) zur Taktung der externen Peripherie bereitgestellt und kann dort oder an TP4 gemessen werden. Fehlt dieser Takt, findet auch keinerlei Signalwechsel auf den Adress- und Datenleitungen statt.

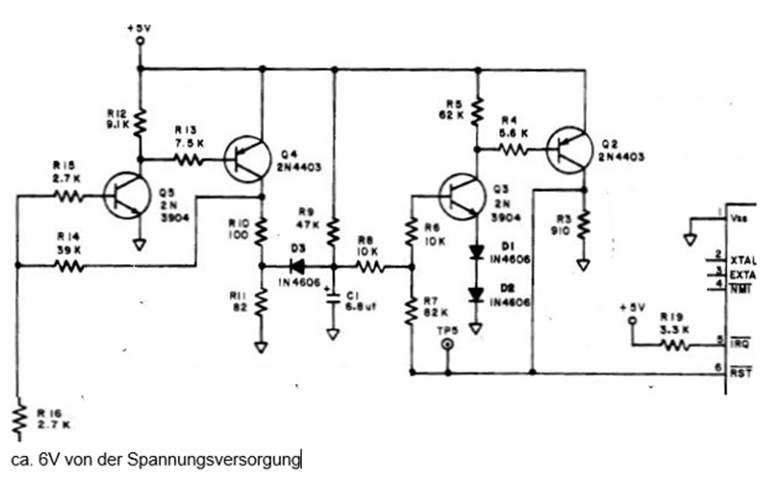

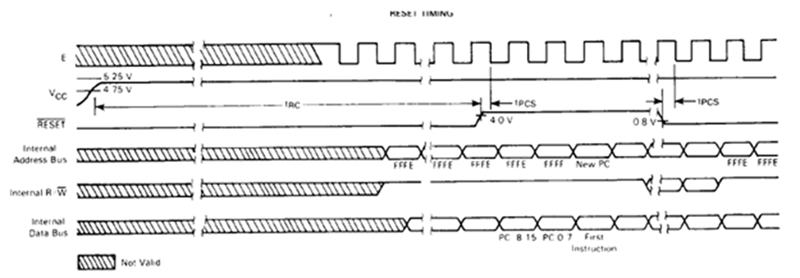

Resetschaltung

Die Resetschaltung gewährleistet, dass die CPU erst startet, nachdem sich nach dem Einschalten eine stabile Versorgungsspannung und die Taktversorgung eingestellt hat. Das wird erreicht, in dem die /Reset-Leitung nach dem Einschalten auf Low-Pegel gelegt und für eine kurze Zeit auf Low-Pegel gehalten wird. Erst nach Ablauf dieser Zeit wechselt der Pegel auf der /Reset-Leitung nach High und die CPU beginnt mit dem Startvorgang. Der Pegel der /Reset-Leitung bzw. der Wechsel kann am TP5 gemessen werden.

Direkt nach dem Einschalten ist der Kondensator C1 noch entladen. Dadurch sperrt Q3 und Q2 schaltet GND (= Low) auf die /Reset-Leitung. Wird C1 über R9 geladen, folgt Q3 dessen Ladekurve bis die Ladespannung ca. 2.5 V erreicht hat. Q2 schaltet und legt um diese Zeit verzögert die /Resetleitung auf +5V (= High). Gleichzeitig wird nach dem Einschalten Q5 angesteuert, der Q4 durchschaltet. Dadurch stellt sich an der Kathode von D3 eine Spannung von etwa 2.5 V ein, was verhindert, dass sich C1 über D3 und R11 entladen kann. Wird die Versorgungsspannung unterbrochen, entlädt sich C1 über diesen Weg, da Q4 nicht mehr durchgesteuert wird. Somit ist ein sauberer Reset auch nach sehr kurzen Spannungsunterbrechungen gewährleistet.

Der MC6803 Prozessor

Im Vergleich zum MC6802 und MC6808, die auf früheren Soundboards Anwendung fanden, hat der MC6803 folgende Besonderheiten, die auf dem CHEAP SQUEAK zum Tragen kommen:

- verschiedene Betriebsmodi, aus denen der für den Einsatzzweck benötigte Modus während des Reset-Vorganges ausgewählt wird

- gemultiplexter Adress- / Datenbus für A0 – A7 und D0 – D7

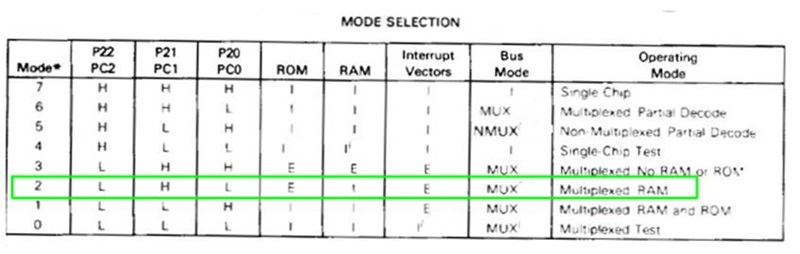

Einstellung des Betriebsmodus:

Wenn man den Schaltplan betrachtet, ist folgendes ersichtlich:

- Das Board verfügt über zwei EPROM Steckplätze. Der Prozessor benötigt somit ein externes ROM.

- Ein externes RAM ist nicht vorhanden, es wird das interne Page-Zero RAM des Prozessors genutzt

- Es ist ein 74LS373 zum demultiplexen der Adress- und Datenleitungen vorhanden

Lt. der Mode Selection Tabelle entspricht diese Konstellation dem Mode 2 des Prozessors, d.h. er muss in diese Betriebsart versetzt werden bevor der Programmablauf startet.

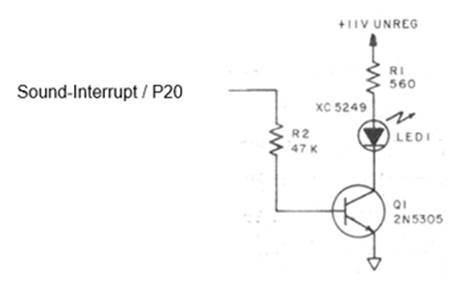

Um nun in den notwendigen Betriebsmodus zu gelangen, muss unmittelbar nach dem Anlegen der Betriebsspannung an den Portleitungen P20, P21 und P22 die Bitkombination L-H-L anliegen.

Nach Ablauf des Reset-Timers und dem damit verbundenen L/H Übergang auf der Reset-Leitung liest der Prozessor diese Bitkombination ein und schaltet in den Mode 2.

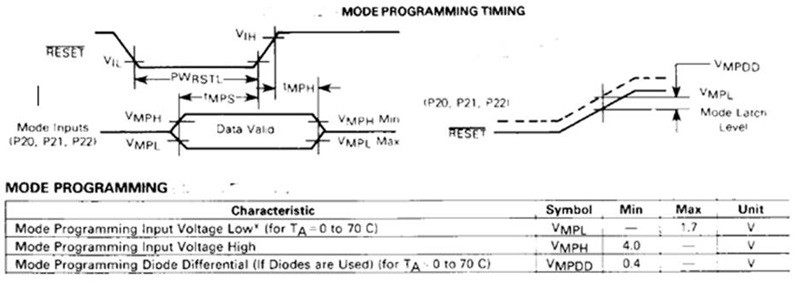

Voraussetzung dafür ist die Einhaltung der Bedingungen entsprechend dem folgenden Diagramm:

- Bedingung: Der Low-Level an den Ports muss um mindestens 0,4V höher liegen, als der Low-Level auf der Reset-Leitung und darf max. 1.7V betragen

- Bedingung: Der High-Level an den Ports muss mindestens 4.0V betragen.

- Bedingung: Der L-H Übergang darf nicht abrupt, sondern muss innerhalb einer /Reset Rise Time von min. 1µs stattfinden.

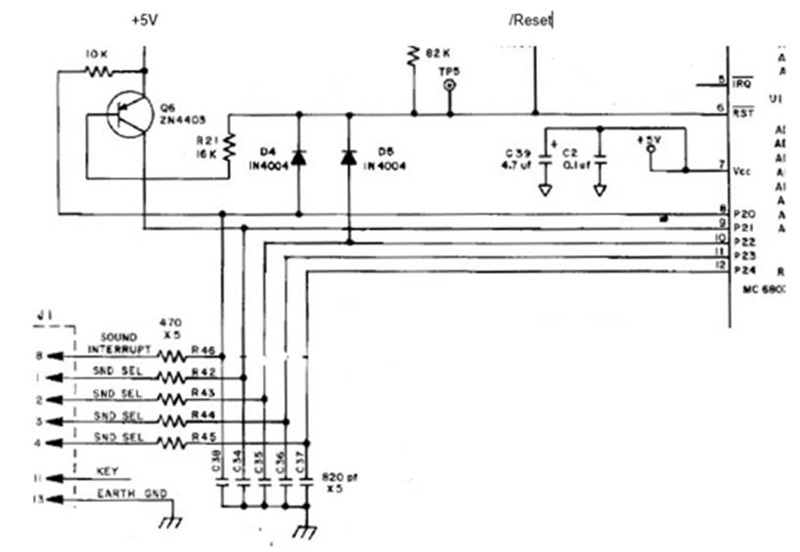

Umsetzung auf dem CHEAP SQEAK:

Nach dem Einschalten der MPU sind die Portleitungen des PIA U11 noch nicht initialisiert und befinden sich in einem hochohmigen Zustand, so dass an der Sound-Interrupt als auch die Sound-Select Leitungen kein Potential seitens der MPU anliegt. Die Reset-Schaltung auf dem CHEAP SQUEAK legt die Reset-Leitung des 6803-Prozessors auf Low-Potential (0V). Port P20 und Port P22 liegen über die Dioden D4 und D5 an der Reset-Leitung. Durch die interne Portbeschaltung von P20 – P22 fällt an beiden Dioden deren Vorwärtsspannung von ca. 0.6V ab. Dieser Wert stellt sich an den beiden Portleitungen ein. Damit ist die erste Bedingung erfüllt.

Das Low-Potential auf der Reset-Leitung schaltet über Q6 High-Potential (+5V) an die Portleitung P21 wodurch auch die zweite Bedingung erfüllt wird. Somit kann der Prozessor beim Ablauf des Reset-Timers die für den Betriebsmodus 2 notwendige Bitkombination L-H-L einlesen und diesen einnehmen.

Die Einhaltung der /Reset Rise Time ist durch das Design der oben beschriebenen Reset-Schaltung gewährleistet.

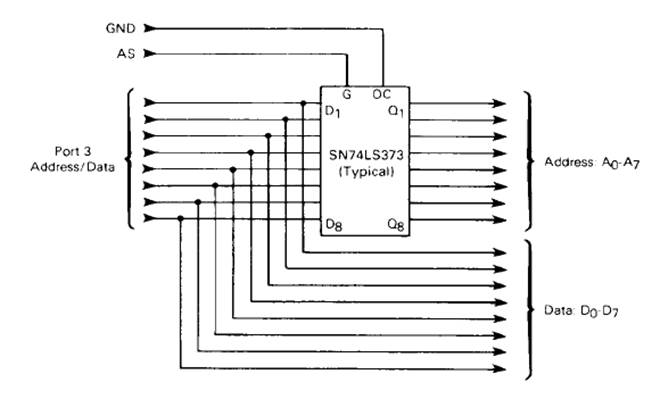

Aufsplitten der gemultiplexten Portleitungen P30-P37

Der MC6803 nutzt im Betriebsmodus 2 die Portleitungen P30 – P37 sowohl für die unteren 8-Adressleitungen A0 – A7 als auch für die Datenleitungen D0 – D7. Wird externe Peripherie, wie bspw. ein ROM angesprochen, muss die Adressinformation auf A0 – A7 gepuffert werden, um direkt im Anschluss die Dateninformation über D0 – D7 senden * bzw. empfangen zu können.

Das geschieht mit Hilfe des Octal Latch 74LS373 (U2).

Ablauf der Adressierung:

Der Prozessor legt die oberen 8 Bit der 16 Bit breiten Adresse an seine Adressleitungen A8 – A15 und die unteren 8 Bit an die Portleitungen P30 – P37. Diese sind mit den Eingängen D1 – D8 des Octal Latch 74LS373 (U2) verbunden. Legt er nun seine AS Leitung auf High Potential, erfolgt die Übernahme der Adressinformation von P30 – P37 in das Latch. Dieses speichert die Information und stellt sie an dessen Ausgang als A0 – A7 zur Verfügung, bis eine neue Adressinformation durch einen erneuten L/H-Wechsel auf AS übernommen wird. Nun sind P30 – P37 wieder frei und werden direkt im Anschluss für den Datenbus D0 – D7 verwendet.

* Anm.: Da der 6803 nur Lesezugriffe auf das ROM durchführen muss, ist die R/W-Leitung nicht beschaltet.

Adressdecodierung:

Die Adressdecodierung erfolgt mittels der drei 3-input NAND Gates eines 74LS10 (U5) und ist damit recht trivial.

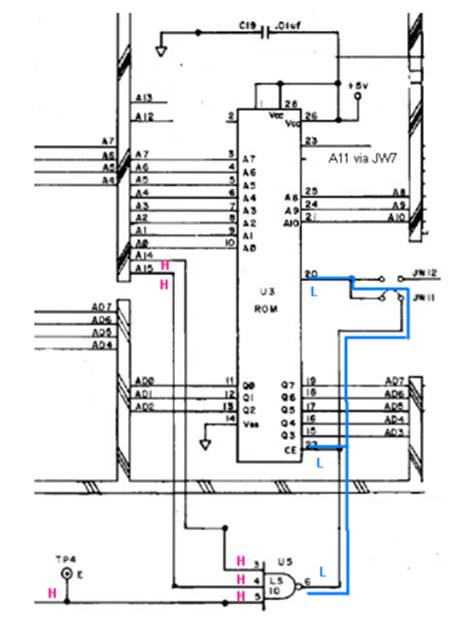

Anhand der folgenden Beispiele soll die Arbeitsweise veranschaulicht werden. Angenommen, in U3 ist ein 2732 EPROM gesteckt und das soll von der CPU adressiert werden. U3 ist das „Boot EPROM“, d.h. es enthält die Startadresse, an der nach dem Einschalten der Betriebsspannung die Programmabarbeitung beginnt. Damit darauf ein Zugriff erfolgen kann, sind folgende Voraussetzungen erforderlich:

Ein 2732 hat eine Kapazität von 4kB. Zur Adressierung dieser 4096 Speicherstellen werden die Adressleitungen A0 - A11 benötigt. Diese sind fest mit dem Adressbus verbunden. Die Freigabe des Chips erfolgt durch einen Low-Pegel an Pin 20 (/CE) als auch an Pin 22 (/OE) des 28 poligen Sockels. Beim 24 poligen 2732 wären das durch das nach unten versetzte Einsetzen Pin 18 (/CE) und Pin 20 (/OE).

Somit stehen für die vollständige Adressierung noch die Adressleitungen A12 – A15 zur Verfügung. A12 und A13 werden für die Adressdekodierung nicht benutzt.

Wie nun der /CE und der /OE Anschluss des 2732 seinen Low-Pegel erhält, wenn die CPU eine dessen Adressen anspricht, zeigt der folgende, auf das wesentliche reduzierte Ausschnitt aus dem Stromlaufplan:

Die CPU kann nur einen Speicherzugriff durchführen, während das Taktsignal auf der E-Leitung High-Pegel führt. Die E-Leitung liegt an einem Eingang des NAND-Gatters von U5. An den anderen beiden Eingängen dieses Gatters liegen die Adressleitungen A14 und A15. Führen alle drei Leitungen (E, A14, A15) einen High-Pegel, dann liegt am Ausgang des NAND-Gatters ein Low-Pegel. Da /CE direkt und /OE über den eingelegten Jumper JW11 mit dem Ausgang des NAND verbunden sind, erfolgt die Freigabe des U3 und die CPU kann einen Lesezugriff über A0 – A11 durchführen.

Somit wird ein 2732 in Position U3 immer adressiert, wenn A14 und A15 High-Pegel führen.

Die Adressdekodierung für ein 2732 EPROM in Position U4 funktioniert auf die gleiche Weise. Die E-Leitung führt High-Pegel und gelangt auf den Eingang eines NAND-Gatters. A15 führt High-Pegel und gelangt an einen weiteren Eingang des NAND-Gatters. A14 gelangt an den dritten Eingang des NAND-Gatters, nachdem dessen Pegel über ein separates NAND-Gatter invertiert wurde. Somit muss A14 Low-Pegel führen, damit /CE von U4 auf Low gelegt werden kann. /OE von U4 wird über JW10 fest mit GND (= Low-Pegel verbunden) und ist somit unabhängig von einer Freigabe über U5.

Für die Adressierung eines 2764 in U3 ist ebenfalls der Zustand A14 und A15 = High erforderlich. Diese beiden Leitungen werden auch in dem Fall zusammen mit der E-Leitung durch ein NAND-Gatter verknüpft. Sind alle drei Leitungen High, gibt das NAND wie bei einem 2732 durch ein LOW auf den /OE-Pin das EPROMs frei. /CS wird über JW12 fest mit GND verbunden und ist somit unabhängig von einer Freigabe über U5. Die zusätzlich benötigte A12-Leitung wird über JW2 an den Sockel geschaltet.

Daraus ergeben sich folgende Basisadressen:

Der Prozessor greift nach dem Einschalten und Ablauf des Reset-Timer auf die Adressen FFFEh und FFFFh zu, an denen sich die Startadresse des abzuarbeitenden Programmes befinden muss. Da die Adressleitungen A12 und A13 bei der Adressdekodierung nicht berücksichtigt werden, ist der Adressraum eines 4k-ROM quasi noch 3x nach oben hin gespiegelt. Bei einem 8k ROM wird A13 nicht berücksichtigt, wodurch dessen Adressraum noch 1x nach oben hin gespiegelt wird. Somit sind bei beiden ROM-Typen die beiden notwendigen Startadressen erreichbar. Für das gesamte ROM ergibt sich der Gesamtadressraum von 8000h – FFFFh.

Im Reset Timing Diagramm ist ersichtlich, dass der Prozessor nach dem Einschalten auf die beiden Adressen FFFEh und FFFFh zugreift, an denen sich die Startadresse für den Programmablauf befindet.

Selbsttest nach dem Einschalten:

Wie bei einigen anderen Bally Boards, auf denen ein 680x Mikroprozessor die Steuerung ausführt, wird auch beim CHEAP SQUEAK eine LED verwendet, um den Status der einzelnen Selbsttest Schritte anzuzeigen. Der Selbsttest wird automatisch nach jedem Einschalten (Power-Up) ausgeführt.

Erstes Aufblitzen der LED (Initial Flicker)

Der 6803 wird während des Resetvorgangs nach dem Einschalten in den Betriebsmodus geschaltet. Die internen Register und I/O-Leitungen werden in einen definierten Zustand gesetzt und der Programmablauf gestartet Während dieser kurzen Zeit wird der Transistor Q1 über R2 angesteuert und schaltet die LED ein. Die programmgesteuerte Initialisierung schaltet die LED wieder aus. Dieses kurze Aufblinken der LED wird als „Initial Flicker“ bezeichnet und sagt aus, dass der 6803 erfolgreich gestartet und der Programmablauf in U3 begonnen hat

Troubleshooting:

Die LED bleibt nach dem Einschalten dunkel:

- Messen, ob die +12 Volt und + 5 Volt Versorgungsspannung an den entsprechenden Testpunkten sowie an den Pins der am Bootvorgang beteiligten IC auf dem CHEAP SQUEAK anliegen.

- Prüfen, ob die oben dargestellte Schaltung zur Steuerung der LED in Ordnung ist und Konnektivität zu P20 und J1 Pin 8 besteht

- Den 6803 aus der Fassung nehmen, die Lötstellen und Kontakte der Fassung überprüfen und den 6803 wieder einsetzen.

Die LED leuchtet nach dem Einschalten dauernd:

- Messen der +5 V Versorgungsspannung (Vcc) gegen Masse (GND) an den am Bootvorgang beteiligten ICs. Die Versorgungsspannung sollte grundsätzlich direkt an den IC-Pins (Vcc gegen GND) gemessen werden.

- Durch fehlende Aktivität auf den Adress- und Datenleitungen z.B. bedingt durch eine defekte CPU (U1) kann keine Peripherie adressiert werden, wodurch auch eine Konfiguration der Portleitungen unmöglich ist.

- Die CPU benötigt zum Abarbeiten der Befehle einen Systemtakt. Dieser wird durch einen 3.58 MHz Schwingquarz, der an den Pins 2 und 3 angeschlossen ist, generiert. Fehlt dieser Takt, findet auch keinerlei Signalwechsel auf den Adress- und Datenleitungen statt, wodurch ein Lesen der ROM-Inhalte und eine Konfiguration der Portleitungen unmöglich ist. (P20 = High-Pegel, LED = an). Intern werden diese 3.58 Mhz durch 4 geteilt, so dass der eigentliche Systemtakt zum Abarbeiten der Befehle 895 kHz beträgt. Dieser Takt wird an Pin 40 (E) zur Taktung der externen Peripherie bereitgestellt. Die Taktsignale können mit Hilfe eins Oszilloskops sichtbar gemessen werden. Steht kein Oszilloskop zur Verfügung, kann mit Hilfe eines Digital-Voltmeters die Spannung an TP4 kontrolliert werden. Durch das Impuls- / Pausenverhältnisses von 1:1 beträgt die an TP4 zu erwartende Spannung ca. +2.5 VDC.

- Die Adressen $FFFE und $FFFF des (EP)ROM auf Position U3 enthalten die Startadresse für den Programmablauf. Auf diese Adressen greift die CPU nach dem Einschalten bzw. einem Reset zu. Daher ist ein Bootvorgang mit einem defekten, fehlenden oder falsch „gejumperten“ U3 nicht möglich. U1 behält in diesem Fall seine Einstellungen nach dessen automatischen Konfiguration nach dem Einschalten. (P20 = High-Pegel, LED = an)

- Fehler in der Reset-Schaltung. Nach dem Einschalten liegt an TP5 Low-Pegel. Nach einer Zeit von ca. 300 ms wechselt der Pegel an TP 5 auf High und gibt somit die CPU frei. Liegt nach dem Einschalten bereits ständig ein High-Pegel ohne vorangegangenem Wechsel nach Low oder ständig ein Low-Pegel ohne Wechsel auf High an, ist die Reset-Schaltung zu prüfen.

- Fehler in der Adressdekodierung um U5. Sobald aus den Daten auf den Adressleitungen Chip-Select- bzw. Output-Enabled Signale für die ROMs generiert werden müssen, legt die CPU bei einem Zugriff auf deren Adressbereich die Enabled-Leitung auf High-Pegel und bestimmt über A15 und A14 welches der beiden ROM über die niederwertigeren Adressleitungen adressiert werden soll. Ein defekter U5 erzeugt keine CS bzw OE Signale und eine fehlende oder fehlerhafte Adressinformation beeinträchtigen den Programmablauf. Eine Überprüfung der CS bzw OE Signale bzw. der Konnektivität der Bus-Signale wäre hier Mittel der Wahl.

- Die CPU benötigt zwingend das RAM in der Page-Zero. Ein defektes RAM verhindert den Start des Programmablaufes. Da das RAM Bestandteil des Prozessors ist, hilft nur ein Tausch von U1.

1. Blinken der LED (ROM U4-Test)

Der erste Schritt der Selbsttest Routine prüft ein gestecktes 4kB ROM auf Steckplatz U4 .Dabei wird eine Checksummen-Prüfung durchgeführt. Entspricht die Summe der ROM-Inhalte nicht der vorgegebenen Checksumme, bleibt das 1. Blinken aus und der Bootvorgang wird abgebrochen.

2. Blinken der LED (ROM U3 Test) = 1. Blinken bei nicht gestecktem U4

Der zweite Schritt der Selbsttest Routine prüft das 4kB bzw. 8kB ROM auf Steckplatz U3. Dabei wird eine Checksummen-Prüfung durchgeführt. Entspricht die Summe der ROM-Inhalte nicht der vorgegebenen Checksumme, bleibt das 2. Blinken aus und der Bootvorgang wird abgebrochen.

3. Blinken der LED (internal RAM Test) = 2. Blinken bei nicht gestecktem U4

Dieser Schritt der Selbsttest Routine prüft den nicht für die CPU selber reservierten Bereich des internen RAM, der sich im Bereich der Page-Zero im Adressbereiches $0020 - $007F befindet. Es wird pro Speicherplatz jeweils 256-mal ein inkrementierender 8 Bit Wert von $00 bis $FF geschrieben und zurück gelesen. Entsprechen die zurück gelesenen Werte exakt den vorher geschriebenen, wird der RAM Test mit dem 3. Blinken der LED quittiert. Entsprechen nicht alle der zurück gelesenen Werte den vorher geschriebenen, bleibt das 3. Blinken aus und der Selbsttest und weitere Bootvorgang des CHEAP SQUEAK wird abgebrochen.

Troubleshooting:

Werden die Selbsttestschritte für den ROM-Test fehlerfrei bestanden ist bei einem fehlerhaften RAM-Test nur der Tausch des 6803 Prozessors zu empfehlen.

Hinweis: Ist das RAM in dem vom Prozessor selbst genutzten Bereich defekt, wird u. U. der ROM-Test als fehlerhaft signalisiert. Daraus folgt, dass ein nicht bestandener U4 und U3 Test nicht zwingend auf ein defektes EPROM hinweist.

Ende des Selbsttest

Nach dem letzten Blinken bleibt die LED an und es wird je nach Modell ein kurzer Testsound abgespielt. Nun ist das CHEAP SQUEAK bereit, Sound-Interrupts vom MPU-Board zu empfangen und die über die Sound Select Leitungen angeforderten Audiosignale zu generieren. Die LED verhält sich je nach eingesetzten Game-ROM unterschiedlich. Bei manchen Modellen bleibt sie generell an, bei anderen erlischt sie kurz, wenn eine Soundanforderung seitens der MPU stattfindet.

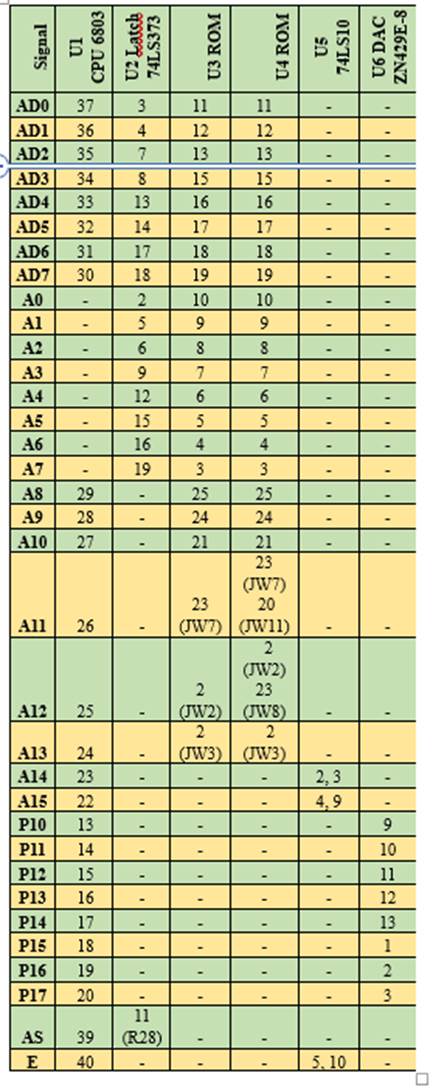

Bus Associated Signals

Die nachstehende Tabelle zeigt die Verbindungen der Bus-Signale zwischen der CPU und den direkt mit dieser verbundenen ICs. Abhängig von dem Ergebnis des Selbsttests können die Verbindungen zwischen den betroffenen Komponenten mit Hilfe eines DMM im Durchgangstest auf Konnektivität oder Berührungen untereinander überprüft werden. Ebenso ist eine Überprüfung im Betrieb mittels eines Logic-Probes hilfreich. An allen in einer Reihe der Tabelle angegebenen Punkten liegt das gleiche Signal bzw. zeitgleich dessen Pegel. Die Klammern geben die Jumper oder Bauteile an, über die das Signal den Pin erreichen kann.

Die nicht aufgeführten Verbindungen zwischen den IC ohne CPU-Bezug können dem Schaltplan entnommen werden und sollten im Fehlerfall ebenfalls auf Konnektivität bzw. Berührung untereinander geprüft werden. Das gilt auch für die Spannungsversorgung der einzelnen IC sowie Pins, die über Jumper mit +5V oder GND verbunden werden können.

Hinweis: Die Verbindungen sollten immer direkt von oben am IC-Anschluss geprüft werden, damit die IC-Sockel und deren Lötstellen in der Überprüfung enthalten sind

Adressierung (Soundauswahl) durch die MPU

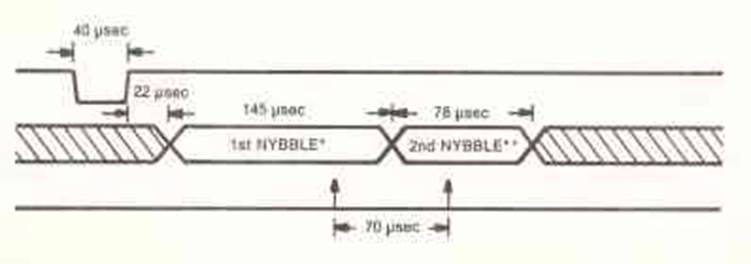

Damit die MPU das CHEAP SQUEAK ansprechen kann um notwendige Steuerinformationen zu übermitteln sowie die zu generierenden Soundsignale anzufordern, generiert sie über die Sound Interrupt Leitung (J1 Pin 8) für die Dauer von 40µs einen Low-Pegel. Es stehen 4 Sound Select Leitungen an J1 (Pins 1,2,3,4) zur Verfügung. Darüber wären bei einer direkten Adressierung nur 16 verschiedene Soundadressen resp. Soundsignale möglich. Um eine erweiterte Adressierung und damit mehr Soundsignale generieren zu können, wird die Soundadresse in der Form von 2 halben Bytes (= 1 Nibble = 4 Bit) innerhalb eines fest definierten Zeitfensters übertragen, was einer Auswahlmöglichkeit zwischen maximal 256 möglichen Steuer- und Soundkombinationen entspricht. Die CPU liest diese 2 Nibble entsprechend des unten dargestellten Timing-Diagrammes zur weiteren Verarbeitung ein.

Diese Art der Adressierung wurde vom Bally Squawk &Talk Module übernommen.

Das Timing für die Adressierung ist in folgender Abbildung dargestellt:

Das obere Signal zeigt die Sound Interrupt Leitung mit dem 40µs andauernden Sound-Interrupt Impuls seitens der MPU. Darunter sind die Sound Select Leitungen dargestellt, über die die MPU 22µs nach dem Interrupt das erste Nibble (LSB) der Sound Select Information für eine Dauer von 145µs bereitstellt. Die Abfrage durch die CPU erfolgt ca. 110µs nachdem die MPU das erste Nibble bereitgestellt hat. Im Anschluss daran wird das zweite Nibble (MSB) für die Dauer von 78µs angelegt und ca. 35µs später durch die CPU abgefragt. Die CPU setzt die beiden Nibbles (MSB + LSB) zu einem Byte zusammen und prüft dessen Wert auf Gültigkeit. Wurde eine ungültige, nicht verwertbare Information empfangen, wird diese verworfen. Ansonsten wird die Information zur Generierung des Soundeffektes weiterverarbeitet. Dabei ist zu beachten: Sollte das CHEAP SQUEAK aufgrund eines Fehlers die Daten nicht in dem vorgesehenen Timing abfragen und dadurch z.B. nur ein Nibble empfangen, könnte sich durchaus ein - für die CPU - gültiger Wert zur Soundauswahl ergeben, was eine falsche Soundausgabe zur Folge hat. Es erfolgt keine Quittierung (z.B. in Form eines Acknowledge) seitens des CHEAP SQUEAK zurück zur MPU ob eine gültige, ungültige oder keine Information empfangen wurde.

Wichtig ist, dass auf diesem Weg keine Daten für die Soundgenerierung von der MPU zum CHEAP SQUEAK gelangen, sondern jeweils nur die Adressierung einer von 256 möglichen Aktionen, Tönen bzw. Audiosequenzen. Dadurch beschränkt sich die Kommunikation zwischen der MPU und dem CHEAP SQUEAK auf ein Minimum.

Beispiel:

Adresse 00000010 erzeugt ein hohes „Ping“. Adresse 00000011 erzeugt ein tiefes „Pong“. Wird nun im Spielablauf nur ein „Ping“ benötigt, addressiert die MPU 00000010. Wird nur ein „Pong“ benötigt, addressiert die MPU 00000011. Wird nacheinander ein „Ping“, „Pong“, „Ping“, „Pong“ benötigt, könnte anstatt der Anforderung von vier einzelnen Soundsignalen auch eine neue Adresse z.B. 00010100 definiert worden sein, anhand der die CPU diese vier Einzelsequenzen durch nur eine Anforderung nacheinander ausführt. In der Praxis werden jedoch direkt hintereinander folgende Töne einzeln angefordert.

Ausnahme ist die Generierung des Background-Sounds. In dem Fall sendet die MPU den Steuerbefehl zur Soundwiederholung gefolgt von der zu wiederholenden Soundsequenz. Diese Sequenz wird dann so lange wiederholt, bis eine neue Soundanforderung eintrifft.

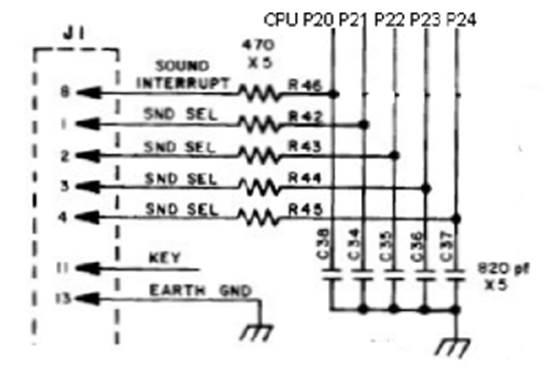

Die an J1 ankommenden Sound Select Signale und der Sound-Interrupt werden über einen 470Ohm Widerstand an die Portleitungen P20 bis P24 der CPU geleitet und dort verarbeitet.

Hinweis: Die Sound Select Leitungen werden durch die PB0 bis PB3 Pins des PIA U11 auf dem MPU-Board gesteuert. Diese Pins steuern gleichzeitig den 1 aus 16 Demultiplexer für die Spulentreiber (momentary solenoids) auf dem Solenoid Driver Board. Die Sound Interrupt Leitung wird durch den CB2 Pin des PIA U11 auf dem MPU-Board angesprochen. Führt diese Leitung Low-Signal, wird das Solenoid Driver Board angesprochen. Nur bei Einhaltung des oben beschriebenen Timings wird das CHEAP SQUEAK adressiert. Liegt zeitgleich eine Anforderung an das Solenoid-Driver-Board zur Aktivierung einer Momentary Solenoid an, wird eine Soundanforderung unterdrückt bzw. im Nachgang gestellt..

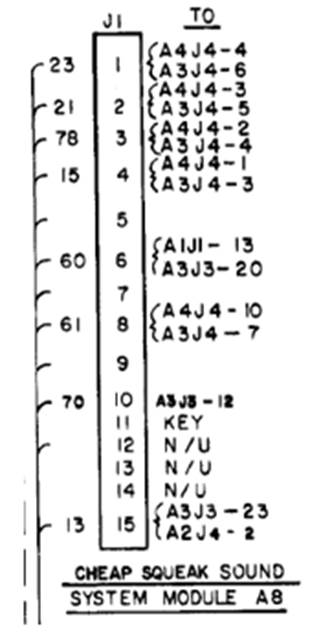

Der Verdrahtungsplan der Geräte, in dem ein CHEAP SQUEAK zum Einsatz kommt, zeigt jeweils, dass die Signalleitungen von der MPU A4 J4 Pins 1,2,3,4,10 zum CHEAP SQUEAK A14 J1 Pins 1,2,3,4,8 und von dort weiter zum SDB A3 J4 Pins 6,5,4,3,7 verlaufen. Wichtig in diesem Zusammenhang ist zu wissen, dass bei einem Fehler an einer oder mehreren Leitungen zwischen MPU und CHEAP SQUEAK nicht nur die Adressierung des CHEAP SQUEAK, sondern gleichzeitig auch die Spulenadressierung fehlerhaft wäre.

Die korrekte Verbindung zwischen MPU und Sound-Board lässt sich mit einer Widerstandsmessung feststellen. Dazu wird im spannungsfreien Zustand der Widerstand der Sound-Interrupt Leitung und den Sound-Select Leitungen zwischen deren Pin am PIA U11 auf der MPU und deren jeweiligen Eingangspin von U1 auf dem Soundboard gemessen. Jede Leitung wird über einen Widerstand auf der MPU, dem dortigen Steckverbinder und dem Kabelbaum zum Sound-Board geführt, um dort wieder über den Steckverbinder und einem Widerstand zu U1 zu gelangen.

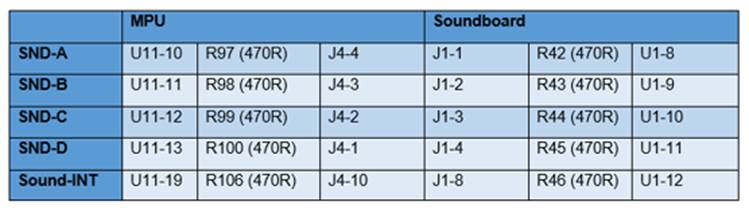

Die folgende Tabelle zeigt den Weg der Leitungen von der Quelle (MPU) bis zum Ziel (SB):

Für die Sound-Select Leitungen A – D und die Sound-Interrupt Leitung ergibt sich bedingt durch die beiden Widerstände ein Streckenwiderstand von jeweils 940 Ohm.

Steht ein AID1 Kit zur Verfügung, lässt sich auch damit die Konnektivität zwischen der MPU und den P20 – P24 Ports der CPU auf dem CHEAP SQUEAK prüfen, auch wenn keine AID-Testpoints im Schaltplan ausgewiesen sind.

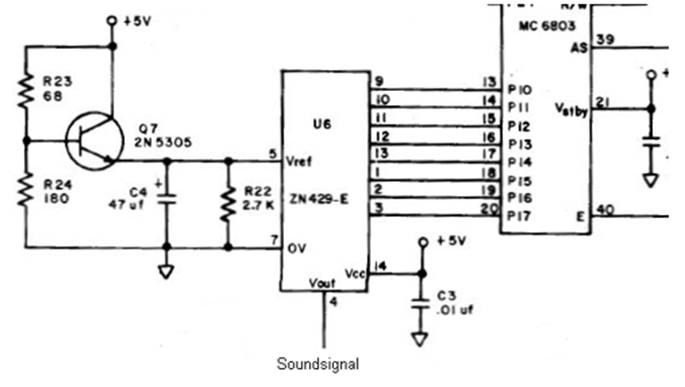

Soundgenerierung:

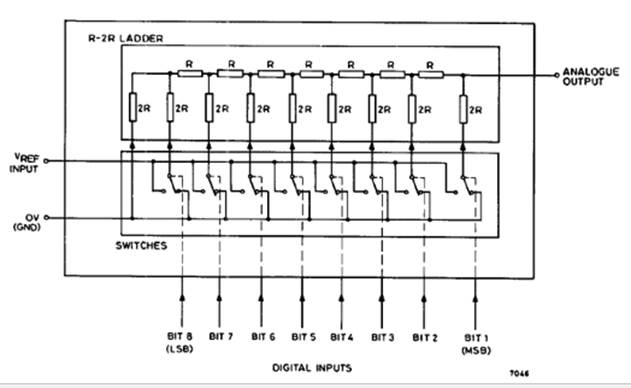

Die Soundgenerierung wird mit Hilfe des Digital/Analog-Wandlers (DAC) ZN429E-8 (U6) realisiert, der aus einem R/2R Netzwerk besteht. Da der DAC nicht im direkt adressierbaren Bereich der CPU liegt sind seine 8 digitalen Eingangsleitungen mit den I/O Ports P10 – P17 der CPU verbunden. Die CPU liest die notwendigen Bytes aus dem Sound-ROM, verarbeitet die darin enthaltenen Informationen zu den auszugebenden Werten und legt diese anschließend an die Portleitungen P10 – P17. Somit sind in den ROMs keine gesampelten und digitalisierten Werte hinterlegt, was den Rahmen deren Speichervolumen sprengen würde. Der DAC wandelt jedes von der CPU generierte Byte in einen, der digitalen Information entsprechenden Spannungswert.

Das R/2R-Netzwerk des DAC besteht aus Widerständen mit zwei unterschiedlichen Werten: Die einzelnen Eingangsbits, hier schematisch als Schalter dargestellt, liegen je nach Schaltungszustand entweder auf Masse oder an der Referenzspannung und speisen einen elektrischen Strom über doppelt so große Widerstände (2R) ein, wie sie im horizontalen Teil (R) des Netzwerks bestehen. Jedes Bit trägt so seinen spezifischen Teil zur resultierenden Ausgangsspannung bei. Das höchstwertige Bit ist für 50 %, das folgende für 25 % das nächste für 12,5 % usw. der Referenzspannung verantwortlich. In Summe ergibt sich eine analoge Spannungsstufe, die dem Wert des digitalen Eingangswertes entspricht. Im Beispiel des ZN429E-8 sind das 256 verschiedene Werte (0-255).

Rechnerisch lässt sich die Ausgangsspannung folgendermaßen ermitteln:

Ausgangsspannung = Referenzspannung / 256 x Digitaler Wert

Beispiele mit einer Referenzspannung von 2.56V:

Digitalwert 0 = 00000000b: Ua = 2,56V / 256 x 0 = 0V

Digitalwert 128 = 10000000b: Ua = 2.56 / 256 x 128 = 1,28V

Digitalwert 200 = 11001000b: Ua = 2.56 / 256 x 200 = 2.00V

Der Auszug zeigt den DAC mit der Anbindung an die Portleitungen P10 – P17 der CPU, über die er die digitale Information erhält. Mit Hilfe von Q7 und dessen Beschaltung wird die Referenzspannung von ca. 2.5 V erzeugt. Diese liegt permanent zwischen den Pins 5 und 7 des DAC an und kann dort gemessen werden. Am Vout Pin 4 steht das Ausgangssignal zur weiteren Verarbeitung bereit. Das ist der Punkt, an dem das Audiosignal als erstes auftritt. Es kann mit einem Oszilloskop gemessen oder mit einem Signalverfolger geprüft werden.

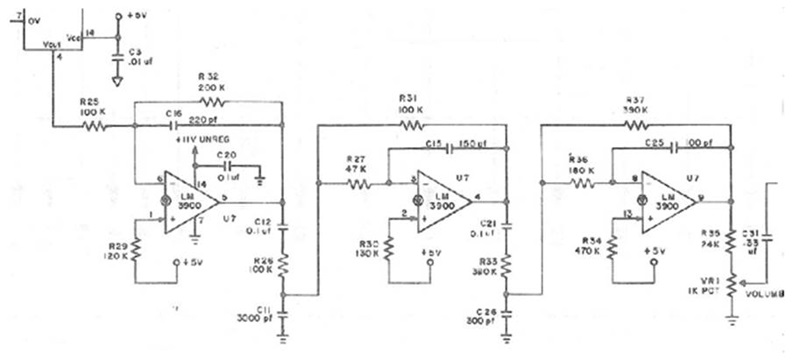

Filterung und Vorverstärkung

Die Umwandlung der Sounddaten durch den DAC hat einen unerwünschten Nebeneffekt zur Folge: „Digital Conversion Noise“. Dabei handelt es sich um Oberwellen, die durch die fehlenden weichen Übergänge zwischen den einzelnen Spannungswerten der generierten Signalkurve entstehen. Um diese Oberwellen zu dämpfen und dadurch ein „kurvigeres“, weniger mit Oberwellen behaftetes Signal zu erhalten, wird das Ausgangssignal des DAC zu einem mehrstufigen Tiefpassfilter / Vorverstärker geleitet, die aus drei der vier Operationsverstärker des LM3900 (U7) und deren Beschaltung aufgebaut ist.

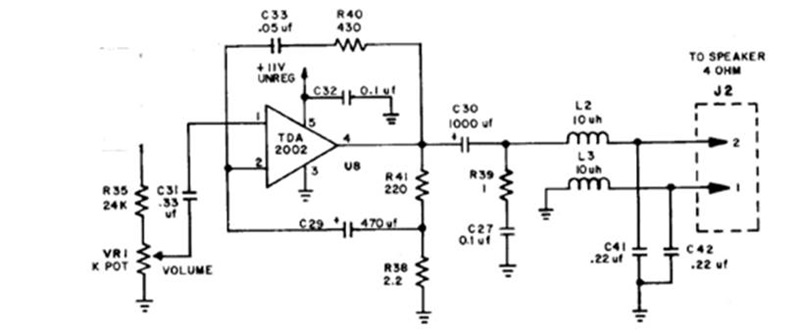

Dieser befindet sich im mittleren rechten Bereich des CHEAP SQUEAK auf dem kleineren der beiden Kühlkörper. Das aufbereitete Audiosignal gelangt über R35, den Lautstärketrimmer VR1 und C31 an den nicht invertierenden Eingang von U8 (TDA2002), Das vom TDA2002 verstärkte Soundsignal wird über den Spannungsteiler R41/R38 und über C29 auf den invertierenden Eingang von U8 zurückgekoppelt und gleichzeitig über C30 und L2 an J2 Pin 2 in Verbindung mit J2 Pin 1 zum Anschluss des 4 Ohm Lautsprechers bereitgestellt. C27 und R39 bilden ein so genanntes Boucherot-Glied oder Snubber-Glied zur Verhinderung von wilden HF-Schwingungen am Ausgang von U8. L2 / C41 und L3 / C42 bilden Tiefpassfilter und blocken ebenfalls hochfrequente Störanteile Richtung Lautstärkepoti in der Kassentür bzw. Lautsprecher.

Der Testswitch:

Im oberen linken Bereich des CHEAP SQUEAK befindet sich ein Test-Switch SW1. Vorausgesetzt das Board hat den Selbsttest nach dem Einschalten erfolgreich durchlaufen, wird nach Drücken des Test-Switch bei den meisten Sound-ROMs eine fest definierte Soundsequenz abgespielt, um die Funktion unabhängig von den Steuersignalen der MPU überprüfen zu können. Das kann abhängig vom Sound-ROM immer die gleiche Sequenz sein oder sie wechselt bei jedem erneuten Druck auf den Test-Switch. Darauf erfolgt ein Warmstart des CHEAP SQUEAK Boards.

Eine unangenehme Eigenschaft kann nach dem Druck auf den Switch auftreten: Der Switch schaltet direkt GND auf den /NMI-Eingang der CPU. Eine Entprellung wurde seitens der Entwickler nicht getroffen, was zur Folge haben kann, dass die CPU bei einem mehrere Jahrzehnte alten Switch bei einem Druck durch die fehlende Entprellung mehrfaches Drücken erkennt. Jedes Mal, wenn die CPU die Interrupt-Anforderung über den /NMI-Pin erhält, werden die Registerinhalte in einem internen Stapelspeicher (Stack) gesichert, ein Interrupt ausgeführt – also der Testsound abgespielt – und danach die Registerinhalte zurückgeschrieben. Erkennt die CPU mehrere /NMI-Anforderungen, werden auch entsprechend oft die Registerinhalte gesichert. Da der Stack nur eine begrenzte Größe aufweist, kann es zu einem Stack-Overflow kommen, der die CPU und damit das gesamte CHEAP SQUEAK zum Absturz bringt, was nur durch Aus- und wieder Einschalten zu beheben ist. Wichtig zu wissen ist, dass es sich bei diesem sehr selten auftretenden Phänomen mehr um eine Fehlfunktion bedingt durch einen Designfehler als um einen Defekt an den elektronischen Komponenten handelt.

Kondensatoren, Stiftleisten, Trimmer

Auf dem CHEAP SQUEAK sind axiale Elektrolytkondensatoren verbaut. Einige Dokumentationen empfehlen als erste Maßnahme zur Fehlerbehebung von Soundproblemen häufig einen Tausch dieser Kondensatoren. Einige Ersatzteilhändler haben die Kondensatoren daher als Komplettset oder Rebuild-Kit in ihrem Angebot. Aber nicht immer ist der Verursacher einer Fehlfunktion beim CHEAP SQUEAK ein gealterter oder ausgetrockneter Elektrolytkondensator. Schon gar nicht ist er die Ursache für zeitweise auftretende Sound-Probleme. Entweder er funktioniert oder er funktioniert halt nicht. Ein Defekt der hochkapazitiven Kondensatoren ist auch nach fast 40 Jahren recht selten. Deren vorsorglicher Tausch ist daher in den meisten Fällen überflüssig. Kondensatoren mit einer geringen Kapazität sind eher betroffen. Da diese Kondensatoren in der Regel als Koppelkondensatoren in den analogen Signalleitungen zwischen den Soundausgängen des DAC und deren nachgeschalteten Filter- und Verstärkerstufen liegen, ist ein Ausfall eines solchen Kondensators mit einem Oszilloskop oder Signalverfolger / -injektor recht schnell zu erkennen. Typische Fehlerbilder: Kein Signaldurchgang oder ein verzerrtes und / oder zu leises Signal. Wird ein kleiner Kondensator als Fehlerquelle identifiziert und muss getauscht werden, sollte man überlegen, ob es wirklich notwendig ist, die anderen Kondensatoren direkt mit auszutauschen, denn jedes unnötige Löten stresst die Lötpunkte, Durchkontaktierungen und Leiterbahnen, was ggf. zu neuen Fehlerbildern führen kann. Bei einem Tausch eines Elkos sollte wieder ein axialer Typ verwendet werden. Mit Drahtstücken verlängerte Anschlussdrähte von radialen Elkos bergen die Gefahr von Berührungen mit ggf. darunter verlaufenden Leiterbahnen.

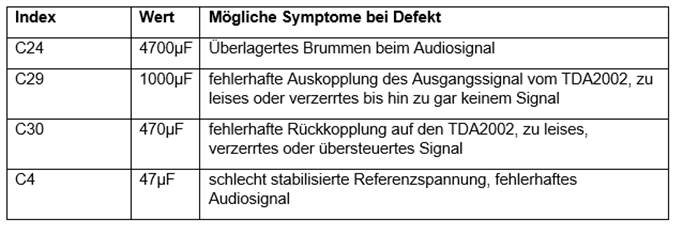

Die nachfolgende Tabelle enthält eine Auflistung der Elkos:

Auf dem CHEAP SQUEAK Board sind einige Tantal Kondensatoren verbaut. Normalerweise sind bei diesen keine Alterungserscheinungen zu erwarten. Es kommt aber gar nicht so selten vor, dass die Tantal Kondensatoren im Bereich vor der +5V Spannungsregelung (C10, C22) infolge einer leichten Überspannung regelrecht abbrennen. Beim Ersatz dieser Tantal Kondensatoren kann man die Überlegung treffen, an deren Stelle Elkos mit einer Spannungsfestigkeit von 35V einzubauen. Deren Kapazität sollte in dem Fall midestens dem doppelten Wert der Tantal Kondensatoren entsprechen, z.B. 10µF.

Bleibt nur der übliche Hinweis auf mögliche Kontaktprobleme zwischen den Platinensteckern und den Stiftleisten nicht fehlen. Nachlassender Kontaktdruck, Schmutz durch Staub, Nikotin- bzw. Teerablagerungen und Korrosion sind nach der langen Zeit häufig die Ursache für zeitweise und damit relativ schwer einzugrenzende Fehler. In diesem Fall ist ein Austausch der Stiftleisten und Platinenstecker (Crimpkontakte) empfehlenswert. Auch die Lötstellen der Stiftleisten sollten nach der langen Zeit auf der Platinenunterseite nachgelötet werden, um Kontaktproblemen durch „kalte“ Lötstellen entgegen zu wirken. Das gleiche gilt für den, in offener Bauweise ausgeführten 10kOhm Trimmer für die Lautstärkeregelung. Ist eine Nachregelung mit Aussetzern und Störgeräuschen verbunden, wird deren Austausch gegen eine geschlossene Bauweise empfohlen.

Fehlersuche im Analogteil mit Hilfe eines Signalverfolgers

Als erste Maßnahme gilt es zu prüfen, ob der Fehler im Digital- oder Analogteil des Boards zu suchen ist. Dazu wird das Gerät in den Zustand versetzt, in dem normalerweise Sound erzeugt wird. Das kann am einfachsten durch Aktivierung des Background-Sound im Testmenü (Step 18 auf 03) und starten eines Spieles erfolgen. Auch die Betätigung von Kontakten hat in der Regel einen Sound zur Folge.

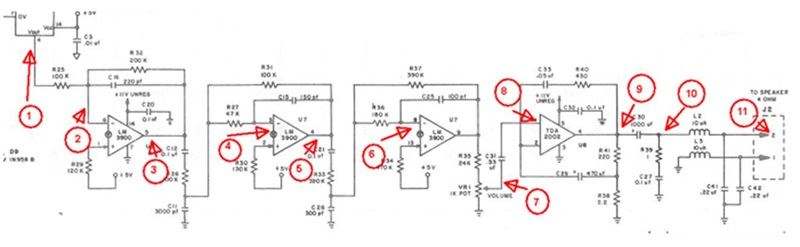

Wie bereits beschrieben wurde, gibt es auf dem CHEAP SQUEAK als analoge Signalquelle den DAC ZN429E. Im nachfolgenden Ausschnitt des Stromlaufplanes sind die Prüfpunkte zum Testen des Signalverlaufes angegeben.

Der Masseanschluss des Signalverfolgers wird mit GND (TP3) des CHEAP SQUEAK verbunden.

Die Verstärkung des Signalverfolgers wird auf minimal gesetzt und eine Soundausgabe gestartet, z.B. durch Drücken des Testswitches oder Spielstart mit aktiviertem Background Sound. Die Prüfspitze wird an den Ausgang des DAC (Pin 4) (= Prüfpunkt 1) gehalten. An diesem Punkt tritt das analoge Signal als erstes auf. Die Verstärkung wird langsam erhöht und dabei geprüft, ob das Soundsignal hörbar wird. Ist dies nicht der Fall, wäre die Prüfung an dieser Stelle schon vorbei und der Fehler im Digitalteil der Schaltung zu suchen.

Ansonsten wird die Prüfung step bystep an den einzelnen Prüfpunkten fortgesetzt.

So kann man sich durch den Verlauf des Signalweges hangeln und an jeder Stelle das Audiosignal bewerten. Allerdings bedarf es etwas Erfahrung, das Ergebnis an den Prüfpunkten 3 – 6 zu bewerten, da gerade bei Filterstufen das Ausgangssignal geringer als das Eingangssignal sein kann. Generell kann man sagen, ist am Eingang der Stufe ein Signal vorhanden und am Ausgang keins, ist der LM3900 sehr verdächtig. Ab Prüfpunkt 7 kann auch die Funktion des Volume Reglers überprüft werden, Je nach Stellung des Trimmers VR1 ändert sich die Lautstärke vom Signalverfolger.

Prüfung der Signalwege mit Hilfe eines Signalinjektors

Eine weitere Möglichkeit zur Überprüfung der Signalwege ist der Einsatz eines Signalinjektors. Dieses Prüfgerät erzeugt ein, in der Amplitude regelbares Signal im hörbaren Frequenzbereich, dass an den o.g. Prüfpunkten in den Signalweg eingespeist (injiziert) und dann über den angeschlossenen Lautsprecher hörbar wird. Zur Prüfung wird der Masseanschluss des Signalinjektors mit dem TP3 (GND) verbunden. Die Amplitude wird auf minimal eingestellt und das Signal mittels der Prüfspitze beginnend am letzten Prüfpunkt vor dem TDA2002 (U8) eingespeist. Ist das Prüfsignal im Lautsprecher hörbar, wird der zu prüfende Signalweg rückwärts in Richtung Signalquelle geprüft, in dem das Prüfsignal an den oben im Schaltplan markierten Prüfpunkten eingespeist wird. Dabei ist jeweils die Amplitude etwas anzupassen. Ist das Signal an einem Prüfpunkt hörbar und an dem davor liegenden Prüfpunkt nicht, liegt der Fehler zwischen diesen beiden Prüfpunkten.

Die Prüfung ist auch in Kombination mit einem Signalverfolger möglich. Dazu wird der Signalverfolger mit einem Prüfpunkt verbunden, der sich nach einem Prüfpunkt befindet, an dem das Signal des Signalinjektors eingespeist wird.

Steht kein Signalinjektor zur Verfügung, lässt sich die Funktion der Signalwege ggf. auch „quick and dirty“ überprüfen. Dazu berührt man mit einem Finger die Anschlüsse der sich im Signalweg befindlichen Kondensatoren, was im Lautsprecher zu einem Netzbrummen führt. Diese Methode stellt allerdings nur einen groben Funktionstest dar und lässt keine Aussage über die Signalqualität zu.

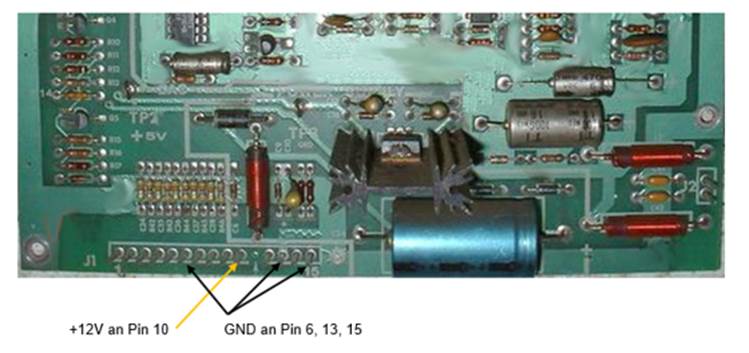

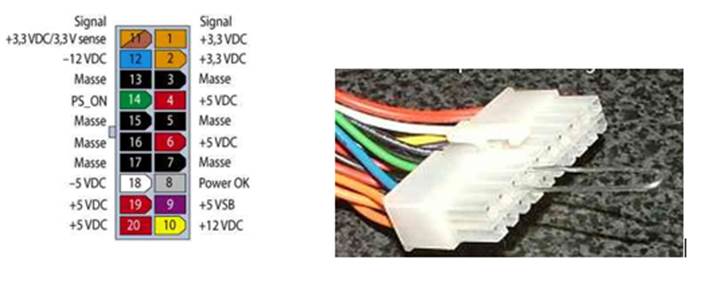

Um das CHEAP SQUEAK auf der Werkbank zu booten, wird eine Gleichspannung von +12 Volt benötigt. Die stellt z.B. ein PC-Netzteil bereit. Die +12V liegen an dem gelben Draht auf Pin 10 des 20-poligen Steckers des PC-Netzteils an. Dieser wird mit J1 Pin 10 des CHEAP SQUEAK verbunden. GND liegt an den schwarzen Drähten des 20-poligen Steckers. Einer dieser Drähte wird mit J1 Pin 6, 13 und 15 des CHEAP SQUEAK verbunden. Damit das Netzteil nach dem Anlegen der Netzspannung die Ausgangsspannungen liefert, muss es über die grüne Steuerleitung (PS_ON) Steckers eingeschaltet werden, in dem diese Leitung mit Masse (schwarz) verbunden wird. Dazu müssten bei einem 20 poligen Mainboard-Stecker Pin 14 mit z.B. Pin 15 gebrückt werden. Es sollte selbstverständlich sein, beide Spannungen vor dem Verbinden mit dem CHEAP SQUEAK zu prüfen. Ein fehlerhaftes Netzteil oder eine, an den falschen Punkten des Steckers abgegriffene oder am CHEAP SQUEAK falsch angelegte Spannung können zu einem Schaden am CHEAP SQUEAK führen.

Hinweis: Manche PC-Netzteile benötigen auf dem +5V Ausgang eine Mindestlast, damit sie auf dem +12V Ausgang eine stabile Spannung bereitstellen.

Nach dem Einschalten der Netzspannung beginnt das CHEAP SQUEAK mit dem Bootvorgang und ist im Idealfall danach in Betrieb. Wird an den Pins 1 und 2 von J2 ein Lautsprecher angeschlossen, ist nach dem Drücken des Testknopfes bei den meisten ROMs eine Soundsequenz zu hören. Bootet das Board nicht oder nicht vollständig, lassen sich auf der Werkbank recht bequem Messungen im Digitalteil des CHEAP SQUEAK anhand der Beschreibungen aus den vorherigen Kapiteln durchführen. Bootet das Board vollständig, können Fehler im Analogteil durch Messungen und Tests mit Hilfe eines Signalverfolgers / Signalinjektors auf dem Weg vom DAC bis zur Endstufe durchgeführt werden. Die Ansteuerung seitens der MPU und deren Verarbeitung ist auf der Werkbank durch das notwendige Timing an der Sound-Interrupt und den Sound-Select Leitungen mit normalen Mitteln sehr eingeschränkt möglich. Es empfiehlt sich zur Funktionsprüfung bzw. Fehlersuche mittels Signalverfolger der Einbau in einen Flipper, der das CHEAP SQUEAK unterstützt.